One of the most exciting things about the future of computing is the ability to process data inside of the memory. This is especially true since the industry has reached the end of Moore’s Law, and scientists and engineers are focused on finding efficient new architectures to overcome the limitations of modern computing systems. Recent advancements in areas such as generative AI are adding even greater pressure to find such solutions.

Most modern computing systems are based on the von Neumann computing architecture. There is a bottleneck that arises in such systems due to the separation of the processing unit and the memory. In the traditional Von-Neuman architecture, 95% of the energy is consumed by the need to transfer data from the processing unit to the memory back and forth. In systems that need fast response, low latency and high bandwidth, designers are moving the memory closer to the CPU so that data doesn’t need to travel as far. Even better is to do the processing within the memory so the data doesn’t need to travel at all. When computing in memory, logic operations are performed directly in the memory without costly data transfer between the memory and a separate processing unit. Such an architecture promises energy efficiency and the potential to overcome the von Neumann bottleneck.

Computing in-memory can be realized using non-volatile devices, with resistive random access memory (ReRAM or RRAM) as an outstanding candidate due to its various advantages in power consumption, speed, durability, and compatibility for 3D integration.

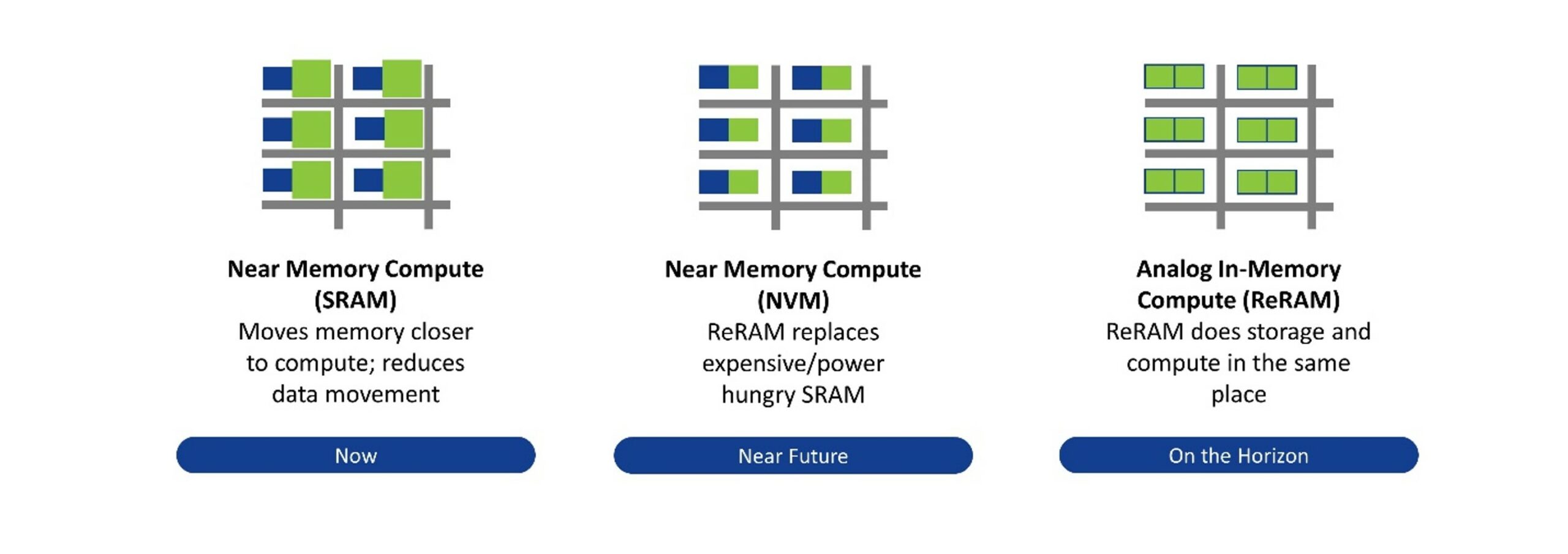

Above: the evolution of compute towards processing in memory

There are various approaches to processing in memory with ReRAM.

One approach for ReRAM-based computing is stateful logic. In this technique, memory cells are used to perform the logic operations without moving any data outside the memory array. The logical states of inputs and outputs are represented as the resistance states of the memristor devices, with logical ’0’ as a High Resistance State (HRS) and logical ’1’ as a Low Resistance State (LRS).

While promising, stateful logic techniques have yet to be demonstrated for large-scale crossbar array implementation. In addition, stateful logic is incompatible with CMOS logic and is limited by a device’s endurance.

Another approach is non-stateful logic. A non-stateful computational operation does not rely on maintaining or remembering the state of previous operations or data. The in-memory logic processes data or performs computations independently of any historical context, performing computations and making decisions quickly for applications such as real-time data processing.

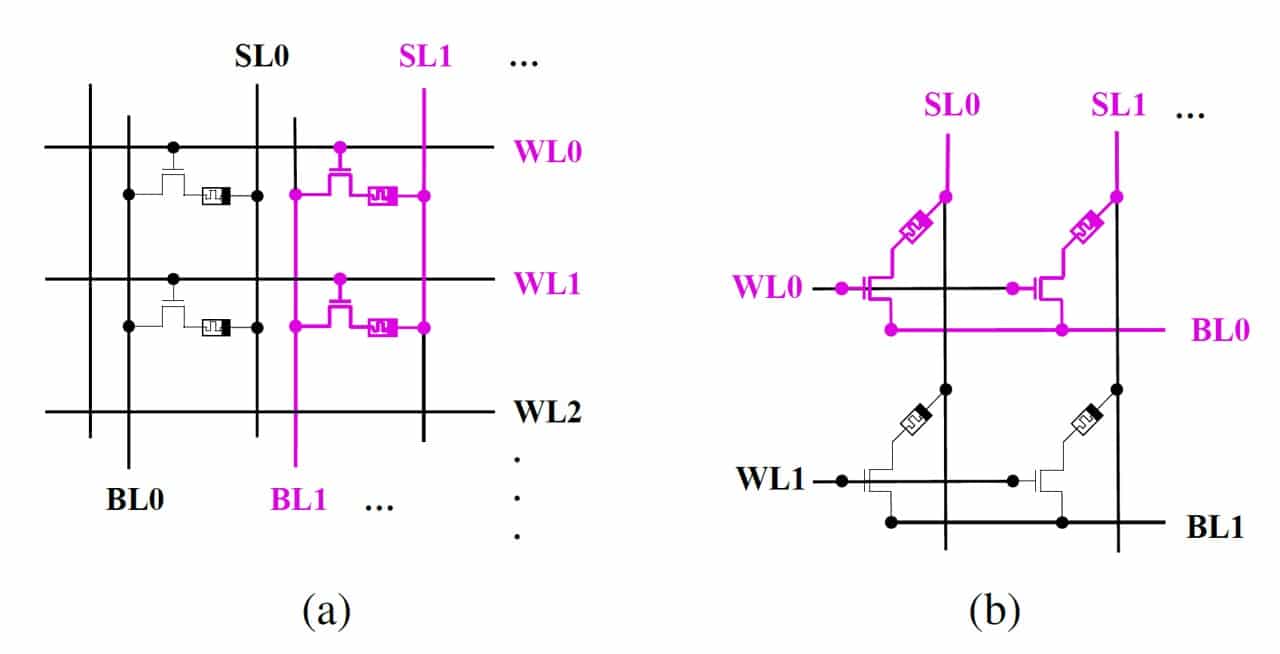

In non-stateful logic, different electrical variables represent their inputs and outputs. For example, the inputs are voltages, and the output is the resistance state of the memristor. Non-stateful logic combines the advantages of computing in-memory with CMOS compatibility. Memristive non-stateful logic techniques can be integrated into a 1T1R memory array, in a similar way to commercial ReRAM products, using a ReRAM like Weebit ReRAM, which is built in a 1T1R configuration where every memory cell has a transistor and a memristive device.

In a new paper by engineers and scientists from Weebit, CEA-Leti and The Technion, “Experimental Demonstration of Non-Stateful In-Memory Logic with 1T1R OxRAM Valence Change Mechanism Memristors,” Weebit ReRAM devices were used to demonstrate two non-stateful logic PIM techniques: Boolean logic with 1T1R and Scouting logic.

The team experimentally demonstrated various logical functions (such as AND, OR and XOR) of the two techniques using Weebit ReRAM to explore their possibilities for various applications. The experiments showed successful operations of both logic types, and correct functionality of the Weebit ReRAM in all cases.

The 1T1R logic technique exhibited notable advantages due to its simplistic design, employing only a single memristor. Scouting logic demonstrated significant potential as it employs a low voltage and no switching during logical operations, promising reduced power consumption and prolonged device lifespan.

Above: Figure 6 from the paper showing the connection of two cells in parallel in an (a) 1T1R standard array and a (b) pseudo-crossbar array

Through additional research and development, the opportunities of this technology will be further explored, ultimately leading to greater efficiency in time and energy. Read the entire paper (with an IEEE subscription) here.