If you’ve ever watched a Formula 1 race, you may have wondered how the cars reach race speeds up to 360km/h (223mph). Part of the magic is of course the very advanced and powerful engines. The design of F1 engines is extremely precise, enabling these sophisticated machines to be compact, lightweight, and highly efficient. However, no less important are all the other elements surrounding the engine that are designed to maximize its efficiency.

Above: A video that breaks down the high-level design of an F1 car.

In the video above, you can see how every single element of each tiny system in the vehicle is painstakingly designed to optimize airflow, decrease heat and weight, maintain a low center of gravity, generate more horsepower, maximize fuel usage, stabilize the driver and, together with the engine, meet the many other goals needed to be an F1 contender. If you’re interested in the math behind how the F1 engines can efficiently reach 1,000 HP, you can check out this video.

While Weebit isn’t designing race cars, we are very focused on optimizing the performance of our ReRAM. As such, we focus not only on the performance of the ReRAM array, but also use a broad range of smart engineering techniques in the Weebit ReRAM module which surrounds our memory array, to maximize that performance.

At the recent 15th IEEE International Memory Workshop (IMW) 2023, Bastien Giraud, a research engineer from CEA-List, presented, “Benefits of Design Assist Techniques on Performances and Reliability of a RRAM Macro,” a new paper written by CEA-List, CEA-Leti and Weebit.

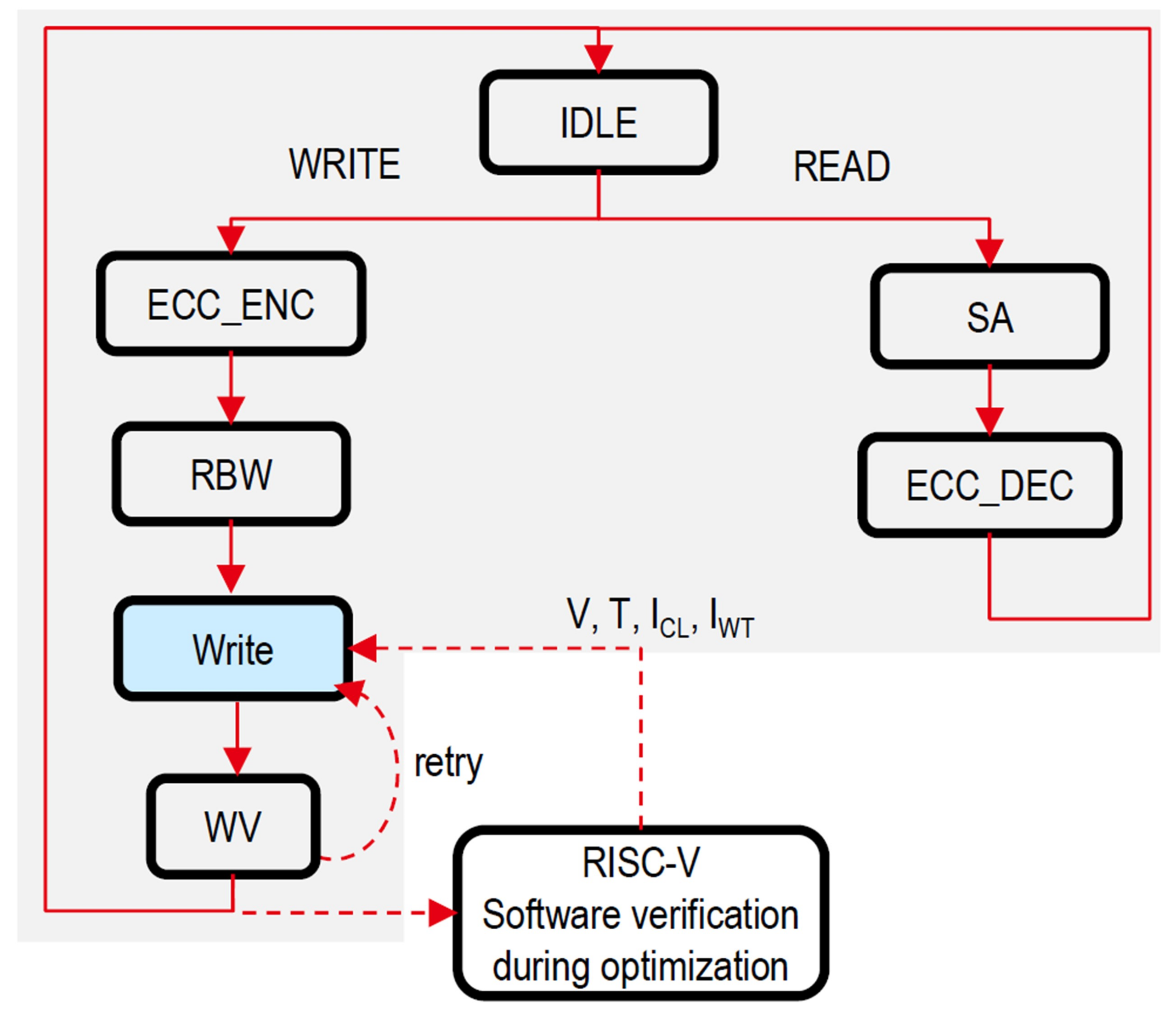

The paper shares various design assist techniques used in development of the Weebit ReRAM module – some of the important methods that help us to optimize performance parameters. This includes state-of-art custom programming strategies including Read-Before-Write (RBW), Current Limiter (CL), Write Termination (WT), Write Verify (WV) and Error Correction Code (ECC), driven by a flexible Smart Write Algorithm (SWA). The authors describe how each one of these techniques enhances the intrinsic performance of the ReRAM.

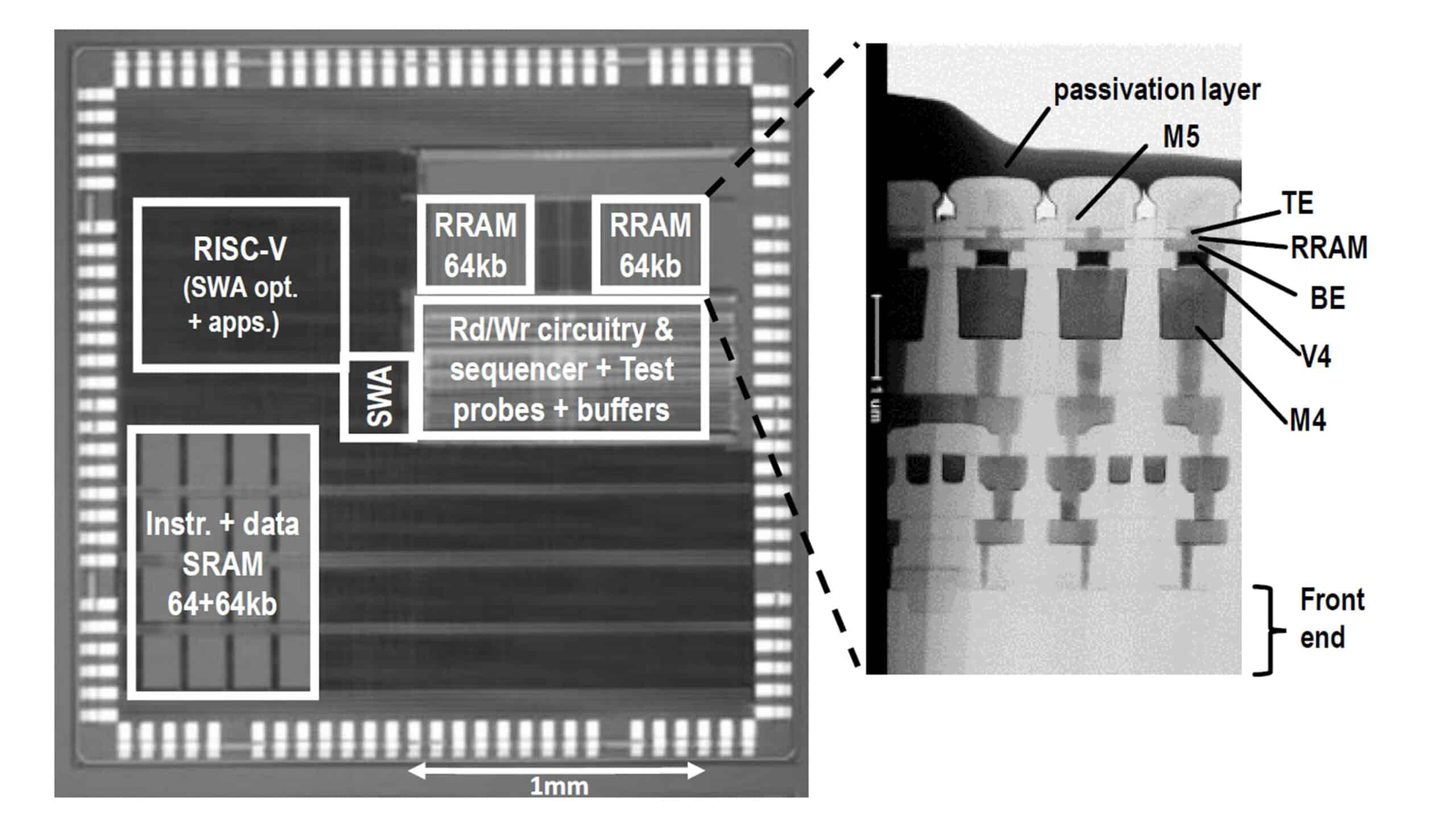

Above: A die photograph and technology cross section of the test chip (memory module) described in the paper.

A key part of the equation is the SWA, which is a programmable algorithm embedded in the design. With the SWA, the writing parameters such as the Set and Reset voltages, the write pulse width, limit current and write termination current can be widely and independently tuned. This means that there is a wide array of different voltages that can be used for Set and Reset (1,024 different combinations). And there is a similarly wide range of pulse width, limitation and termination settings, as well as other variables – all to enable the best possible combinations for a target application. The parameters are programmable to adapt the SWA patterns to the specific requirements.

For testing purposes, the ReRAM module was integrated into a test chip which emulates system functions. Within the test chip, a RISC-V core optimizes the SWA parameters with software tuning loops during early life of the chip, and the ReRAM itself stores the parameters afterwards. This level of flexibility enables each setting to be determined individually to maximize reliability.

Above: a diagram of the embedded SWA.

The paper explores the individual and cumulative benefits from most common programming techniques deployed in the ReRAM macro. Each technique acts differently on energy consumption, access time, bit error rate (BER) and read margin. And altogether, the techniques, mastered from the flexible smart programming algorithm, efficiently counteracts the inherent variability of the ReRAM.

Compared to the original performance of the ReRAM macro, using the combined design techniques resulted in overall improvements of 87% in energy savings and a reduction of 55% on access time. You can read the paper here.

As we get ready for the next Formula 1 races, and as the teams from Alfa Romeo, AlphaTauri, Alpine, Aston Martin, Ferarri, Haas F1, McLaren, Mercedes, Red Bull Racing, and Williams continue to tweak their car designs, at Weebit we are continuing to explore and implement design techniques to further optimize our ReRAM performance.